# Computer System Organization

The B5700/B6700 Series

#### ACM MONOGRAPH SERIES

Published under the auspices of the Association for Computing Machinery Inc.

Editor ROBERT L. ASHENHURST The University of Chicago

- A. FINERMAN (Ed.) University Education in Computing Science, 1968

- A. GINZBURG Algebraic Theory of Automata, 1968

- E. F. CODD Cellular Automata, 1968

- G. ERNST AND A. NEWELL GPS: A Case Study in Generality and Problem Solving, 1969

- M. A. GAVRILOV AND A. D. ZAKREVSKII (Eds.) LYaPAS: A Programming Language for Logic and Coding Algorithms, 1969

- THEODOR D. STERLING, EDGAR A. BERING, JR., SEYMOUR V. POLLACK, AND HERBERT VAUGHAN, JR. (Eds.) Visual Prosthesis: The Interdisciplinary Dialogue, 1971

JOHN R. RICE (Ed.) Mathematical Software, 1971

ELLIOTT I. ORGANICK Computer System Organization: The B5700/B6700 Series, 1973

In preparation

ARTO SALOMAA Formal Languages

NEIL D. JONES Computability Theory: An Introduction

HARVEY ABRAMSON Theory and Application of a Bottom-Up Syntax-Directed Translator

Previously published and available from The Macmillan Company, New York City

V. KRYLOV Approximate Calculation of Integrals (Translated by A. H. Stroud), 1962

# Computer System Organization

The B5700/B6700 Series

# ELLIOTT I. ORGANICK

Division of Computer Science University of Utah Salt Lake City, Utah

ACADEMIC PRESS 1973 New York and London

Copyright © 1973, by Academic Press, Inc. all rights reserved. No part of this publication may be reproduced or transmitted in any form or by any means, electronic or mechanical, including photocopy, recording, or any information storage and retrieval system, without permission in writing from the publisher.

ACADEMIC PRESS, INC. 111 Fifth Avenue, New York, New York 10003

United Kingdom Edition published by ACADEMIC PRESS, INC. (LONDON) LTD. 24/28 Oval Road, London NW1

LIBRARY OF CONGRESS CATALOG CARD NUMBER: 72-88334

PRINTED IN THE UNITED STATES OF AMERICA

# Contents

i

| Preface |                                                | vii |

|---------|------------------------------------------------|-----|

|         | 1 An Overview                                  | 1   |

|         | 2 Block-Structured Processes and the B6700 Job | 9   |

|         | 3 Basic Data Structures for B6700 Algorithms   |     |

| 3.1     | Introduction                                   | 17  |

| 3.2     | Operand Stacks                                 | 22  |

| 3.3     | Treatment of System Intrinsics                 | 25  |

| 3.4     | Block Exits and Returns                        | 26  |

| 3.5     | Procedures Calls—General                       |     |

| 3.6     | Hardware Interrupts as Hardware-Fabricated     |     |

|         | Procedure Calls                                | 31  |

| 3.7     | Small Working Sets                             | 32  |

| 3.8     | Sharing Programs and Data                      | 35  |

|         | 4 Tasking                                      |     |

| 4.1     | Creation and Coordination of Tasks             | 37  |

|         |                                                |     |

| 4.2 | Task Attributes      | 44 |

|-----|----------------------|----|

| 4.3 | Illustrative Problem | 50 |

|     |                      |    |

#### CONTENTS

# 5 Stack Structure and Stack Ownership

| 5.1 | The Critical Block Concept         | 57 |

|-----|------------------------------------|----|

| 5.2 | Dependent versus Independent Tasks | 60 |

## 6 Software Interrupts

| 6.1 | Introduction                                    | 63 |

|-----|-------------------------------------------------|----|

| 6.2 | An Illustrative Example                         | 65 |

| 6.3 | Data Structures for Software Interrupts         | 69 |

| 6.4 | Interrupting a Sleeping Task and Other Problems | 73 |

| 6.5 | Resource-Oriented Synchronizing Primitives      | 75 |

| 6.6 | Software Interrupt Caveats                      | 76 |

## 7 On Storage Control Strategies

| 7.1 | Storage Control at Block Exit | 77 |

|-----|-------------------------------|----|

| 7.2 | Preventing Dangling Pointers  | 78 |

#### 8 The B6700: Pros and Cons

| 8.1 | Introduction                                 | 83 |

|-----|----------------------------------------------|----|

| 8.2 | User Languages and User Program Performance  | 83 |

| 8.3 | The Operating System                         | 89 |

| 8.4 | Hardware Limitations and Future Improvements | 90 |

## 9 Some Hardware Details of Procedure Entry and Return and Tasking

| 9.1 | Overview                             | 93  |

|-----|--------------------------------------|-----|

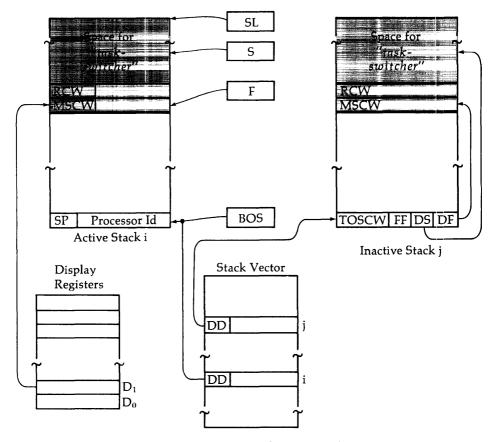

| 9.2 | The Stack Vector                     | 95  |

| 9.3 | Information and Addressing Structure | 95  |

| 9.4 | Stack Build-Up and Procedure Entry   | 99  |

| 9.5 | Hardware Interrupts                  | 111 |

| 9.6 | Multiple Processors                  | 111 |

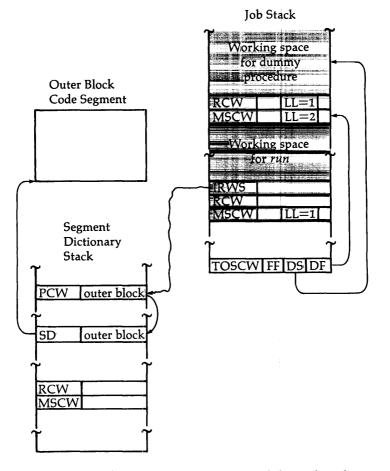

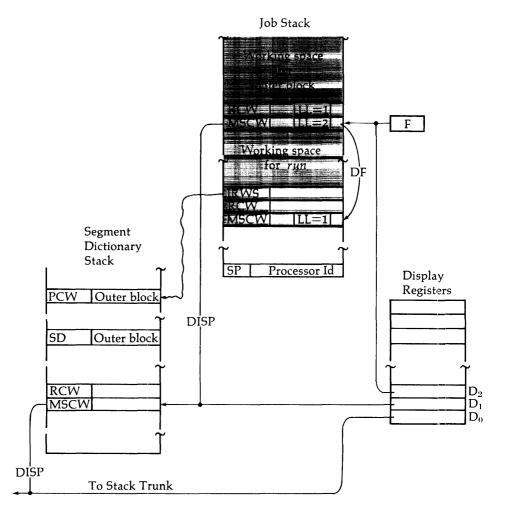

| 9.7 | Job and Task Initiation              | 111 |

|     |                                      |     |

|     |                                      |     |

| Bibliography | 121 |

|--------------|-----|

| Index        | 127 |

# Preface

In 1961, the Burroughs Corporation began producing a line of large scale computers whose organization was radically different from conventional von Neumann computers. From the beginning, these machines have both stimulated and puzzled many who attempted to study them, partially due to inadequacies in the needed factual and expository literature about their internal structure.

The development began with a system called the B5000. A subsequent modification was called the B5500. In 1969, a major advance over the original system was completed and called the B6500. Since then, the B5500, which was still in production, and the B6500 were renamed the B5700 and B6700, respectively.

The structure of these highly innovative systems was widely publicized, but, lamentably, not well understood. Since 1968, however, when some technical descriptions of the B6500 system began to appear in the professional literature, interest has widened, reflecting I believe, a growing concern for the fact that conventional computer organization has remained relatively unstructured—with the objective of being "general purpose"—in the face of an increasing appreciation that certain information structures are characteristic of the computations we normally perform with computers. In short, the looming question has been: How can (or should) computer systems be organized to support, and hence make more efficient, the running of computer programs that evolve with characteristically similar information structures? (The body of this book is an attempt to make this idea more concrete.)

In many types of computer systems, increasing use is being made of virtual storage, which was one of the innovations of the B5000 System and has been an intrinsic part of the design of all subsequent Burroughs systems. I hope readers of this book will gain an historical perspective as well as a technical view of the Burroughs interpretation and implementation of this important concept.

I have aimed the book at an audience consisting of computer center directors, other computer professionals, and serious students in computer science who have an interest in the subject of computer organization. Although not designed as a textbook, this work may well serve for part of the reading in a senior or graduate course in computer system organization. Chapter 1 outlines the book's plan, so that one can decide, after reading this overview, if the material is likely to serve as suitable text material for such a course. I think it will.

A word of caution is perhaps in order for my readers. I have tried to avoid unprovable claims and have made a reasonable effort to delete from the manuscript unjustifiable adjectives of praise for the B5700/B6700 design. Nevertheless, this book retains a natural enthusiasm for the systems it describes. Complete objectivity in any study or exposition of this sort may be a goal that is achievable in an asymptotic sense only. Each reader must therefore apply his own "discount factor" in judging the merits of the opinions and conclusions that I have expressed here.

This book has benefited from the valuable assistance of many members of the Burroughs team who participated in the design and implementation of the B5700/B6700 systems. I especially wish to acknowledge the help received from David Bauerle, Stephen Billard, J. G. Cleary, Benjamin Dent, John Keiser, and Don Lyle. I also wish to thank the Burroughs Corporation management, especially R. R. Johnson and J. F. Kalbach, for the opportunity and support to make this study, and R. S. Barton, my colleague at the University of Utah, who served the role of effective catalyst. This book is published with the permission of the Burroughs Corporation. In undertaking the study on which it was based, I did not underestimate its PREFACE

difficulty, and make no pretense now that the book will prove as helpful to others as it has been for me. If indeed this effort does what I have set out to do, much of the credit should go to the reader, his patience, and his willingness to learn. CHAPTER 1

# An Overview

For the past ten years the Burroughs Corporation has been designing and producing computer systems whose organization and whose hardware/software designs have been significantly different and daring. These Burroughs systems have exhibited an organization consistent with a powerful semantic model for program execution, one that reflects a control structure (flow of control and addressing relationships) that is natural for, and hence one that facilitates, the execution of algorithms.

Spurred by the birth of Algol 60 [44], the last decade was one in which great strides were made in understanding and exploiting the potential of block-structured programming languages for representing complex algorithms, including large and small software systems [18, 21, 27]. Much has been learned about algorithms and ways to represent them in some fashion that would be optimal from the point of view of the man-program interface. With the exception of work on APL and related languages, nearly all recent work on syntactical and semantic design of programming languages has been based on the Algol 60 premise that (static) block structuring of algorithms, i.e., nested declarations, is a natural, if not requisite, form for the expression of complex algorithms (PL/1 [34], Euler [61], Algol 68 [60], Gedanken [51], PAL [62], ..., Burroughs extended Algol [12]). With the exception of isolated computer designs (KDF9 [22], Rice #2 [52], and SYMBOL [15, 20, 53, 55]), few computer systems besides the Burroughs have yet to seriously cater for execution of algorithms expressed in such languages.\*

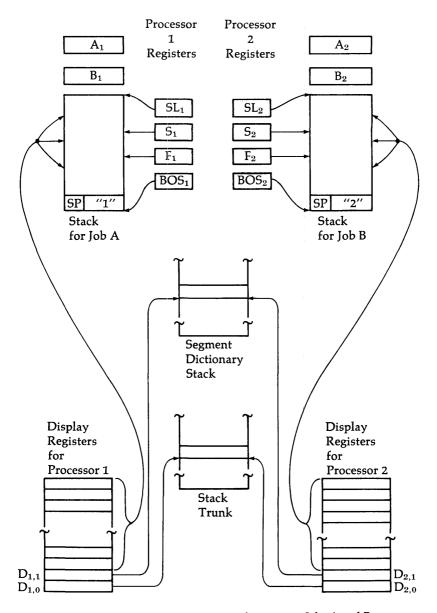

Interestingly enough, the same Burroughs systems have been among the first to offer effective multiprogramming and multiprocessing—a goal of all of today's large computer systems and most smaller ones.

The Burroughs designers viewed the algorithms for their operating systems as inherently block structured and chose to code these algorithms in a language (an Algol 60 extension) that could reflect the structure. While to some others this choice may have appeared to impose unnecessary constraints for system development, the resulting products, measured in terms of throughput and flexibility (and related customer satisfaction), suggests that design "constraints" may really have been design opportunities [17].

The software/hardware developments of the B5700/B6700 progression have in the author's view anticipated (or at least kept pace with) the natural growth in sophistication of our view of algorithmic processes, and that view of algorithms has grown as a direct result of successful efforts of Burroughs and others to design, then further understand, then redesign, etc. very large programs, especially operating systems and information utilities.

It was common in the early 1960's to teach (in universities) that an algorithm is a sequence of procedural steps which, when coded in a higher level Algol-like language, could be structured as a set of nested blocks that defined the scopes of the algorithm's identifiers and dynamic resource requirements when executed on a computer. It may well be common in the 1970's, thanks to the efforts of computer science educators and researchers, and operating system and information utility designers [2, 4, 6, 8, 13, 14, 16, 24–27, 30, 32, 37, 39, 46–48, 54, 56, 58] that we shall teach programming by stressing that an algorithm is a structure (often nested) of interdependent, normally asynchronous tasks, the task being the entity that models the 1960's view of an algorithm. The coding of an

\* The language APL [36] and close relatives such as LCC exhibit dynamic rather than static block structuring and as such are considered outside the scope of this book. Several research groups have reported on their efforts to build computer systems that cater for execution of algorithms in such languages [1, 7, 31, 57] and these are of interest.

Stat 19 get it was an

#### AN OVERVIEW

individual task exhibits a structure that resembles in every respect an Algol (or PL/1) procedure but might also have additional steps to create, destroy, or synchronize with other such tasks.

The Burroughs B5700/B6700 "progression" appears to have had as a major design goal the efficient execution of such algorithmic structures. It behooves (us) educators and scientists to ascertain the importance of this design goal and the extent to which Burroughs may already have achieved it-not just for the benefit of its operating systems but, by simple recursion, for the benefit of the system's users at any subsystem level. The principal purpose of this book is to offer through informal exposition a hopefully revealing and fresh perspective of the B6700 (and by back reference the B5700), its general design and design rationale, and its relative potential as a computer system. The B6700 represents in some sense a best display (i.e., an improved representation) of the corresponding ideas in the B5700. In other respects, such as memory size and raw speed, the B5700 is simply a more limited version of the B6700. For this reason no explicit discussion of the B5700 and its comparison with the B6700 will be undertaken in this relatively short treatment. By a proper whetting of appetites, however, it is hoped to excite the reader into an activated state of inquiry for pursuing further study of the B6700, its predecessor, the B5700, and its probable successors [2, 3, 8, 10, 12, 13, 14, 16, 21, 32, 47, 48].

The B6700 hardware/software architecture is interesting from a number of different points of view—not the least of which are its I/O hardware subsystem [48] and its information flow connections (I/O crossbar matrix) between static (memory) modules and active (processor) units. Again, for the sake of brevity these aspects are not discussed since we proceed on the assumption that such features remain merely sidelights while the reader is still gaining a clear understanding and an appreciation of the B6700's central control structure, the why of it, and the how of it.

As early as 1964, the B5700 operating system was a productive multiprogramming and multiprocessing system operating with only a 32,000 word memory and one or two processors. Starting from significantly different architectural designs, others have toiled to achieve or exceed Burroughs' success, sometimes on systems having far greater speed [18, 42, 43, 46, 56]. During this period

much has been learned about the technology and the underlying principles that govern multiprogramming and multiprocessing. Among the significant and perhaps best applied of these principles have been those based on the program property of *locality* and the consequent notion of the working set [23].

A program that exhibits a high locality of reference is one that "favors" a relatively small subset of its address spaces; i.e., in any given section of virtual time, an executing program is likely to make references within a comparatively small subset of the program segments. This subset is called the working set. (A more formal definition of locality and working set has been given [23], but for our purpose we are content with the above informal expressions.) Denning has shown that the number of independent programs that can be effectively multiprogrammed in a fixed size memory, i.e., without undue thrashing, can then be expected to increase as working sets (and the space required for them) decrease. Experience has shown [46, 59] that multiprogramming improves if the working sets of active processes can be (continuously) monitored and maintained in core memory when they execute. There are several points of interest regarding working sets of B5700/B6700 computations that are worth thinking (and perhaps speculating) about.

- 1. They exhibit strong locality. Working sets of such computations are therefore made relatively easy to maintain in memory while the task is active, because the procedures and the data components of the computation's information structure are the logical subdivisions identified by the programmer.

- 2. The effective size of the working set tends to approach the theoretical size [i.e., the actual amount of core required to contain the working set tends to approach the (theoretical) minimum amount of core required]. This is because:

- (a) the computation's local data structure which grows and shrinks as needed is always kept in core memory while the computation is active;

- (b) only those code segments of the algorithm which are currently being accessed by the processors must be kept in memory while the computation is active;

#### AN OVERVIEW

- (c) apart from certain system routines and tables shared by all active computations, the only other portion of the computation's information structure that must be kept in memory while the computation is active is a dictionary whose entries point to all of the computation's code segments. It is mainly the presence of this dictionary, normally small for small programs, which makes the effective working set exceed the (theoretical) minimum amount of core required.

- 3. The processing cost for making demand insertions of new items (segments), possibly to replace others that are no longer in the working set, appears to approach lowest possible values. (By "lowest possible" we refer to the number of logical addressing steps and not necessarily (physical) speed of processing.) This is because when a nonpresent code or data object must be obtained from secondary storage, the so-called "descriptor" that is accessed by the hardware to reach the desired target contains (directly) the address of the target in auxiliary memory, and not an address of an address, such as an address of a table that is to be searched for the desired address.

If the author is correct in guessing that the B6700/B5700 hardware structure and selected storage representations offer these attractive properties in the maintenance of working sets, it is small wonder that effective resource utilization in these systems has been notable, and that throughput relative to that of the less-structured competing systems of comparable speed (and comparable I/O facilities, etc.) has been advantageous. Put another way, it becomes important to pursue the conjecture that architectural design based on rational (semantic) models for the structure of computational processes, whose algorithms and records of execution are thought of and represented as nested structures, leads to computer systems with more effective resource utilization. The conjecture becomes even more interesting if it is the case that related factors associated with computer use, such as programming (and reprogramming) and the cost of program information sharing, protection, etc., not only do not suffer in tradeoff for the above multiprogramming advantages, but in fact strongly benefit from this design.

It is hoped that the reader will let his natural curiosity take him through the rest of this monograph and then on to further study of the B5700/B6700 so that he can draw his own conclusions.

The design for the remainder of this monograph is as follows: we give a stagewise (top down) exposition of the B6700 control structure to show how algorithms are represented and executed. For this purpose, a series of cases is exhibited, then discussed. Each case includes snapshots of an algorithm at several (interesting) points in its execution. The snapshot is discussed in terms of the revealing conceptual model recently proposed by Johnston [37] (called the contour model), which helps us to focus on the structure of the algorithm (the invariant code part), the structure of the current "record" or state of its execution, the state of the processor, and the interrelationships among them. The series of cases and discussions is designed to impart a cumulative (although by no means complete) understanding of the B6700's control structure as an implementation of a general model for algorithm execution.

As we proceed, we shall discuss several ramifications of this hardware and supporting software architecture, pointing out some of its relative advantages and limitations. Although no explicit comparisons with other systems are given, it is hoped that readers who study the Burroughs concept and implementation of segmentation, the resultant form of virtual memory, and the implications for certain types of controlled sharing of information will then find it easier to make their own meaningful comparisons with corresponding concepts in other systems (e.g., Multics [18, 46]). The same remark applies to comparisons that can be made with the tasking and interprogram communication facilities of other systems [4, 30, 42, 45, 56].

The case studies alluded to above are covered in Chapters 2–6. Chapter 7 considers one potential limitation of the B6700, a discussion of which is motivated in the preceding chapters, while Chapter 8 considers certain other limitations actual and alleged and the system modifications that would remove such limitations. Chapter 9 provides a more complete (and more detailed) view of B6700 hardware for those who will have found themselves ready for a deeper study.

#### AN OVERVIEW

The reader may have observed that this lengthy introduction is in danger of being concluded without mention of the word "stack." We remedy this situation here by observing that the hardware stack structures of the B5700/B6700 have been the key implementation device for achieving hardware support for efficient and controlled execution of algorithms. There can hardly be a reader of this book who is not somewhat aware that stack mechanisms exist in the B5700/B6700. However, many of our readers may not fully recognize how effectively Burroughs has been able to employ stack hardware to reflect an algorithm's static structure, and its execution record, and to build supporting hardware that exploits this storage representation for efficient execution, for recursive operating control, and for minimizing resource consumption.

#### CHAPTER 2

# Block-Structured Processes and the B6700 Job

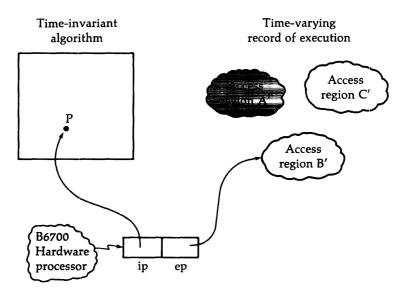

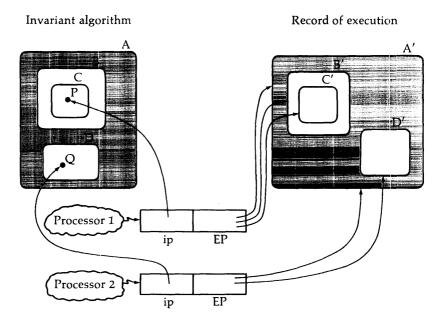

We start by grasping the concept of a B6700 *job*, which consists of a time-invariant algorithm<sup>\*</sup> and a time-varying data structure which is the *record of execution* of that algorithm (Figure 2.1). The algorithm consists of a set of nonvarying code segments which are directly addressable (in the virtual memory sense).

The record of execution is a multipurpose data structure which at any given time defines

- (a) the execution state of the job, including values for all variables (scalar, arrayed, and structured);

- (b) the addressing environment (virtual address subspace) that a hardware processor serving this job may access, or possibly several (overlapping) addressing environments, in case it is appropriate that more than one processor be permitted to execute in the job at the same time (multiple activity);

- (c) the interblock/interprocedure/intertask flow of control history (e.g., chain of calls).

In its simplest view the hardware processor functions by maintaining a pair of pointers, an instruction pointer, *ip*, and an environ-

\* In a more advanced view of a job, new code components might be attached to the algorithm during the course of its execution, but no component would vary (internally) in time.

Figure 2.1 Snapshot of a B6700 job in execution. Schematic view No. 1.

ment pointer, ep, for referencing the accessible portions of the record.

Figure 2.1 suggests that the processor's instruction pointer is about to execute instruction P while the environment pointer, which points to region B' of the record, provides access to data in region B' during execution of P. Figure 2.1 implies that at some subsequent and/or previous point in time ep might point to any of the other access regions of the record.

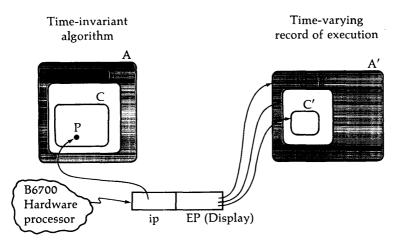

Now, all B6700 programming is done in languages that are compiled in the block-structured sense,\* explicit examples of which are Algol and PL/1. For this reason, the concept of disjoint access regions suggested in Figure 2.1 is, in an important sense, underconstrained. A more authentic view is given in Figure 2.2, which suggests that the B6700 processor's accessing environment is a type of union of access regions, say of C', B', and A'. The nesting of these regions mirrors the nesting of program blocks, each defining the scopes (i.e., range of validity) of program identifiers.

\* Languages like Fortran may define only nonnested program blocks. Such languages can be regarded as degenerate examples of block-structured languages.

Figure 2.2 Snapshot of a B6700 job in execution. Schematic view No. 2.

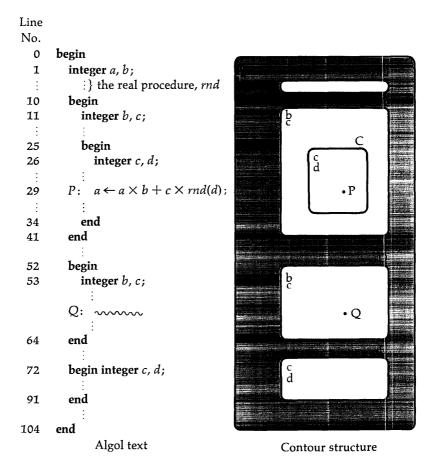

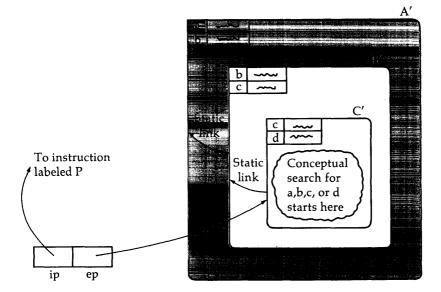

Figure 2.3, for instance, shows the block structure and declarations of an illustrative Algol program. To the right of the program a "contour" schematic suggests an alternative representation that thrusts into bolder relief the scopes of the declared identifiers. Figure 2.2 can be regarded as a snapshot taken when the B6700 processor is about to execute an instruction at the statement labeled P of the program of Figure 2.3. This snapshot suggests that the environment pointer, now shown as a display, EP, which is a vector of pointers, will point to the record regions C', B', and A'. (The concept of display will be treated momentarily.) These access regions of course correspond respectively to sections (blocks) of the program whose corresponding scopes (contours) are named C, B, and A. [A prime-labeling convention (e.g., A' and A) is adopted to relate record contours to their corresponding code blocks.]

Cells associated with the identifiers c and d are contained in region C'; the cell for b is contained in region B', and the cell for a is contained in region A'. These cells are effectively accessed by name.

In the conceptual approach we may well view a reference to a, while executing the statement labeled P, to be a quest for the cell allocated for a. Such a search can be satisfied by an outward scan of the record regions C', B', and A', terminating on the first en-

*Figure 2.3* Block structure and declarations of an Algol program with corresponding contour structure.

counter of a cell named a. Likewise, a search for b will succeed during a scan of B'. Note how the cell named b in A' is therefore quite "invisible" (and therefore inaccessible) to the processor when it is executing the instructions at P. Figure 2.4 is an enlargement of the schematic record of execution shown in Figure 2.2 to show the cells allocated for all identifiers at that particular stage of execution.

Record of execution

*Figure 2.4* Record of execution while the program is executing at the statement labeled *P*. Contour model view in detail.

Of course, in the actual implementation no search is required because each identifier is renamed as an (i, j) pair, where i is a block height (nesting level in the program) and j is an ordinal number that refers to the jth identifier declared in the block [50].

A program may gain a second site of activity by asking for execution of a designated procedure as a task rather than as a subroutine. Figure 2.5 illustrates this concept in contour model terms and suggests how two (or more) processors may share the same code and (parts of) the same record of execution. The accessing environment for the second processor is defined by the display pointing to record regions D' and A', assuming the ip points to the instruction labeled Q shown in Figure 2.3.

Since region A' is common to the environments of the two processors, some locking discipline for achieving mutual exclusion is assumed to be employed. Programs that can support two (or more)

*Figure 2.5* Snapshot of a B6700 job in execution with two processors. Contour model view.

processors have been called multiple activity algorithms [38]. Although an operating system is itself probably the best known and most important example of such algorithms, our case study approach is mainly confined to simpler examples.

A program that can support two (or more) processors need not have allocated to it more than one actual processor in order to execute effectively. A single processor can be shared among (scheduled to serve at) several sites of activity, first being assigned to execute at one site, then at another, etc., achieving the same effect as if there were concurrent execution at several sites but at greater elapsed time.

A program can still be viewed as one involving multiple processors (one per site of activity), as suggested in Figure 2.5, if one regards these processors as virtual (or pseudo) processors. Each such virtual processor is then simply a datum that defines a site of activity and that maps onto the hardware register structure of an actual processor whenever the latter is scheduled to execute at that particular site of activity. Put another way, an actual processor can be "passed around" among the virtual processors as needed, using an effective scheduling discipline. In the B6700 the "activation," i.e., assignment, of a virtual processor to an actual processor (and vice versa) is accomplished by a single instruction.

#### Tasks

Most of the simple programs we write (certainly those we have been accustomed to writing) never have more than one site of activity (at a time). The flow of control is sequential. The site of activity, i.e., the pair (ip, EP), changes dynamically, but one such (ip, EP) pair is sufficient to define the process' state of execution. Procedure calls and returns (recursive or otherwise), as well as coroutine calls and returns (recursive or otherwise) fall in this category of single site of activity. A second (or third, etc.) site is created when a program executes a designated procedure as a *task*. Completion of the task is one way that a site of execution may be terminated (destroyed). Tasks may also be temporarily suspended so they may later be reactivated.

The discipline surrounding the management of sites of activity, i.e., tasking, is discussed at some length in later portions of this book. In the terminology of tasking, the snapshot in Figure 2.5 can be interpreted in the following manner: The principal task is executing at program point P with access environments C', B', A'; a secondary or "offspring" task, spawned at some prior stage of the program's execution (perhaps as a call to create and execute a task at line 28 of the program in Figure 2.3) is now executing at program point Q with accessing environments D', A'.

## CHAPTER 3

# Basic Data Structures for B6700 Algorithms

#### 3.1 INTRODUCTION

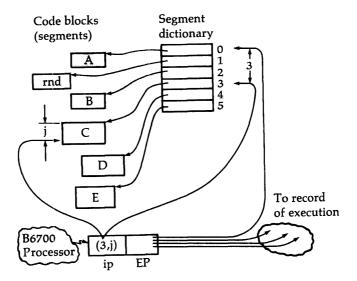

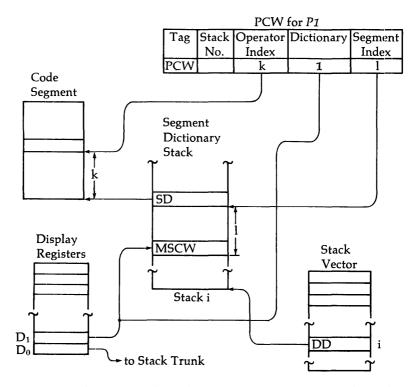

We are now ready for a closer look at the B6700 data structures that are suggested in Figures 2.2 and 2.5. The code for a B6700 algorithm is segmented into blocks, as suggested in Figure 3.1. Each block-structured language has its own syntax for use in delimiting such blocks. (Algol 60, for example, uses begin, end pairs for program blocks and **procedure**, "; " pairs for procedure blocks.) The code for each block is stored as a physically separate segment. Each entry in the segment dictionary serves as a segment pointer (or descriptor.) Only segments which are actually part of the specification of a site of activity (i.e., for an active processor) need be present in physically addressable memory. [All segments of the algorithm are, of course, present in the virtual memory of the algorithm. A "presence" bit in each segment dictionary entry is sensed by the hardware address-formation mechanism. If this bit is off when the descriptor is accessed, a hardware interrupt occurs which delays further execution of the algorithm until the system locates the desired segment (normally) in auxiliary storage and transfers it to addressable core memory.]

When the flow of control moves from one segment to another in the algorithm, the hardware accesses the segment dictionary to acquire the base address of the desired segment as found in its de-

Figure 3.1 Showing how the code for an algorithm is physically segmented into blocks, each block pointed to by a descriptor in the segment dictionary.

scriptor. Thereafter each succeeding instruction in the same segment is accessed as an offset from this base. At first, we show the ip as a 2-tuple, the first component (3 in this case) being the offset into the segment dictionary, and the second component (j) as the offset within the segment. (Later the ip will be represented as a triple.) Thus, line "29" in Figure 2.3 can be thought of as being mapped by the compiler to the pair (3, j). Figure 3.1 suggests how the base address of the segment dictionary is determined, i.e., via a pointer that is pragmatically regarded as being part of the display "bundle."

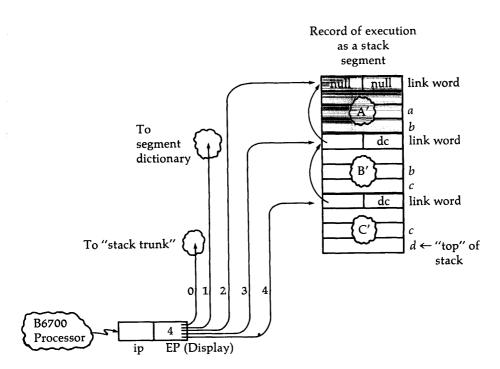

The B6700 data structure for a record of execution takes the form of a stack structure. Figure 3.2 shows the stack structure for the record suggested in Figure 2.2. Stacks in this book are drawn so that they grow downward rather than in the more conventional (cafeteria style) upward direction. Nevertheless, we shall still refer to the cell containing the most-recently stacked element as the "top" of the stack and to the cell containing the least-recently stacked element as the base or "bottom" of the stack. This depar-

Figure 3.2 Snapshot taken while executing at point P in the algorithm of Figure 2.3.

ture from convention allows one to gain a more direct visual correspondence between the growth of the stack and the normal topto-bottom instruction sequence of a block-structured program text.

There are three sections in the stack corresponding to the three contours of the current access environment for the instruction P. Randell and Russell, in the description of their Algol 60 implementation [50] call each stack section an *activation record*. Whenever execution enters a new block of the program, another activation record is allocated in the stack segment and appended (i.e., pushed) on to the top of the stack and back-threaded via *link words* to predecessor records in two ways. One thread (the static chain) shows the static linking of the records, i.e., to define the nesting of environments. The second thread (the dynamic chain), whose ele-

ments are denoted as *dc*, is not drawn explicitly but would, coincidentally, in this case be similar to the static chain. Upon block exit or procedure return, the accessing environment must be restored (reset) so that the topmost activation record designated by the EP bundle is that for execution in the immediately containing block or in the calling procedure, respectively. Links in the dynamic chain provide the information necessary for the processor to make this environment adjustment (including deallocation of activation records) when executing block exits and/or procedure returns.

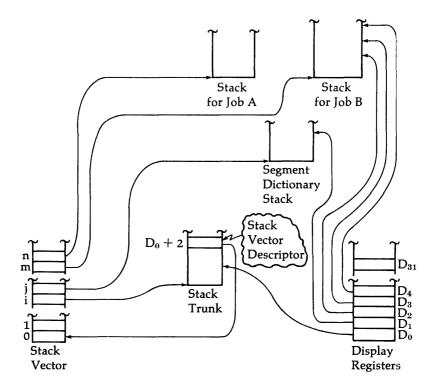

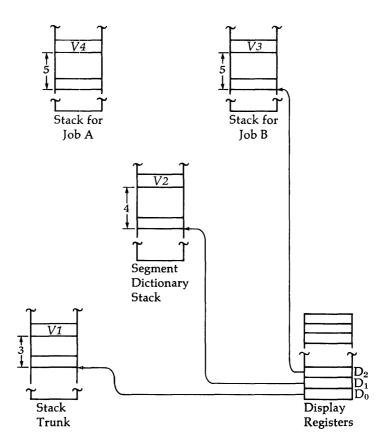

As for the two *additional* display components, one points to the segment dictionary—as already mentioned—while the other points to the base of another area that is related to the work of the system's supervisor. This area, termed *stack trunk* [14] contains, among other things, the descriptors of all the supervisory code segments and system tables. For example, interrupt handlers whose descriptors reside in the stack trunk are accessed through the display pointer to the stack trunk. As a convenience, a simple, standard indexing scheme is used to distinguish the particular display elements. Thus, D<sub>0</sub> is the name for the stack trunk pointer; D<sub>1</sub> is the name for the segment dictionary pointer; D<sub>2</sub>, D<sub>3</sub>, and D<sub>4</sub> in this case serve as pointers to activation records that define the rest of the processor's accessing environment (i.e., regions A', B', and C').

Note, therefore, that the record level associated with the outermost block of any algorithm is always (arbitrarily) 2. The number 4 shown in the EP display box of Figure 3.2 simply signifies the index of the highest nonnull display pointer, there being 32 elements ( $D_0$  through  $D_{31}$ ) in the actual hardware display vector.

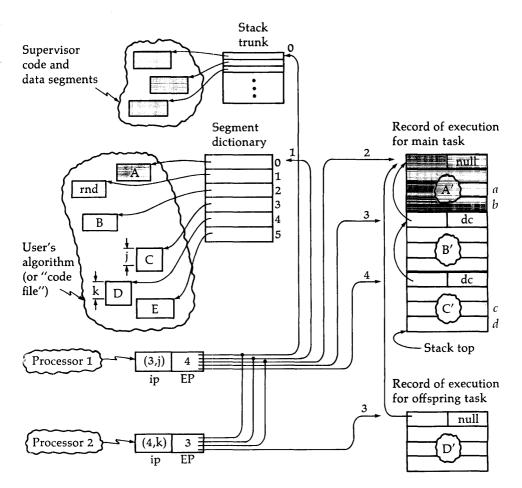

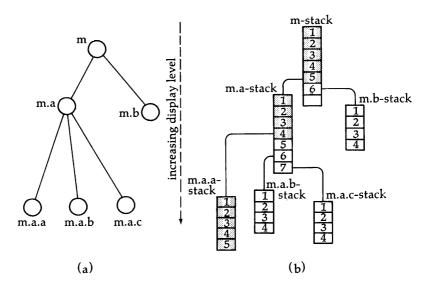

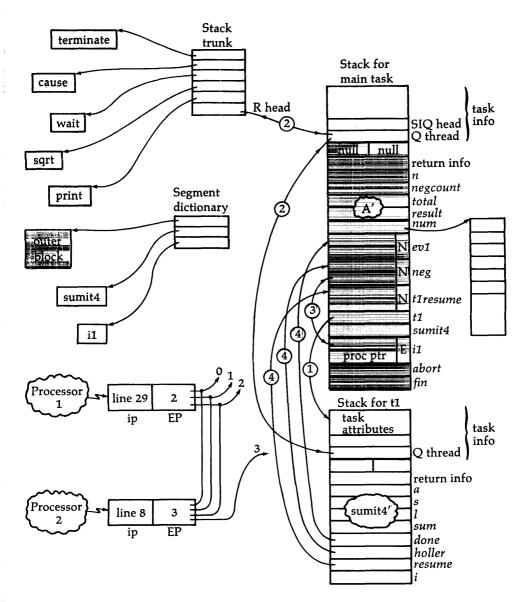

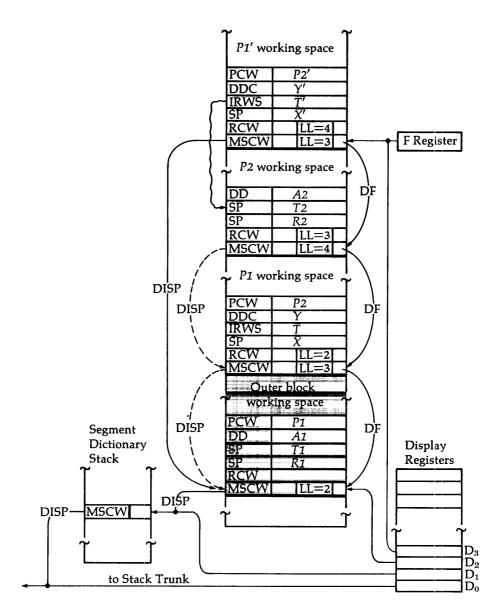

Figure 3.3 is a composite view of the algorithm, the stack structure, and the processors for the execution stage depicted in Figure 2.5. Examining this figure will provide us with additional preview of the subject of tasking that is treated in the next chapter. A few points may be noted.

The activation record associated with execution by the offspring task in the block called D is back-threaded via static link to the record for block A. Display register values are redundant but highly accessible copies of the static link values. Indeed, whenever a virtual processor is mapped onto an actual processor [i.e., whenever a processing unit is "awarded" to a task (site of activity) so

#### 3.1 INTRODUCTION

Figure 3.3 B6700 data structure showing the algorithm, and its structured record of execution, now consisting of two stacks, the segment dictionary, and the stack trunk. Display vectors of the two processors point to addressing environments "topped" by activation records for C' and D' at (display) levels 4 and 3, respectively. The first three display vector elements in each vector have identical values.

it can execute], the display registers for that processor are loaded by copying the static links. [Only the address of the topmost element in the display vector is not a copy of a static link. Only this address, therefore, need be saved as status from the display whenever an actual processor is awarded to another task within the same job or (to a task of another job).] Because record D' has no dynamic antecedent (also true of A'), its dynamic (chain) back pointer is (conceptually) null.

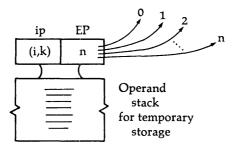

#### 3.2 OPERAND STACKS

Our data structure view of the B6700 is still considerably oversimplified. For one thing, we have not considered the fact that every processor needs some scratch pad memory space for holding operands that are intermediate results needed to evaluate expressions. How much space is needed for such a processor-related purpose is dependent on the complexity of the expression. Compilers, of course, can determine in advance the amount of temporary storage that would be needed for any one simple expression evaluation. Note, however, that any *digression* in the middle of the expression evaluation, say to compute the value of some function to be used as an operand, will force some sort of a pushdown of the temporaries developed thus far so as to "make room" for new temporaries that may be required to compute a function value. For example, in the expression  $a \times b + c \times f(g)$ , where  $f(g) = k \times g + u \times v$ , if evaluation proceeds from left to right, then at the very least the temporary, t1, representing the value of  $a \times b$ , would have to be saved while the processor was producing a value for f(g), evaluation of which requires its own temporary storage.

At the conceptual level the problem of where to save the temporaries may be solved by associating a separate pushdown stack with each virtual processor, as suggested in Figure 3.4. In any actual implementation of this concept, however, it is attractive to employ the top portion of the "current" activation record as an operand stack, and this is indeed the approach taken in the B5700/B6700 implementation. We illustrate by again considering the statement labeled P in the program suggested by Figure 2.3. That statement is

$$P: a \leftarrow a \times b + c \times rnd(d);$$

where *rnd* is a random-number-generating function that is assumed to be a function procedure declared as a separate block (but not shown) in lines 2–10. Executing a reference to *rnd* causes compilergenerated code to create a new activation record, thereby saving the processor's temporaries for use upon return from *rnd*.

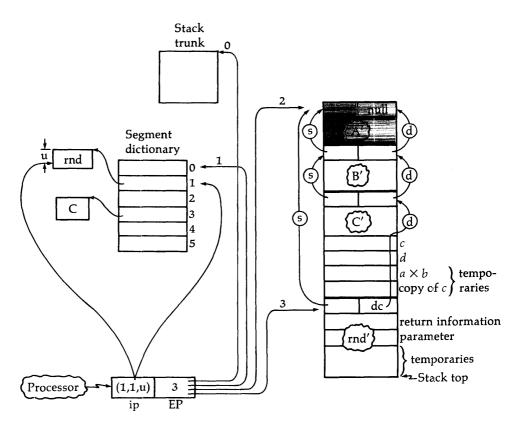

Figure 3.5 is an elaboration of Figure 3.2 to suggest the new condition of the stack segment while executing in rnd. Here we lift the curtain to reveal a few more of the details in the B6700 data structure. In doing so, we gain as a byproduct an introductory exposition of procedure calls, a topic that is developed further in the next two subsections.

First, notice that the activation record for *rnd* is indicated as containing *return information* (first entry after the record's link word). To return to a caller, a processor needs a *return label*, which is in essence a 2-tuple, of the form (ip, ep). Here ip is the position in the program that is one instruction beyond the point of call, and ep is a pointer to the (topmost) activation record employed by the caller. In returning to block C, the processor must also be able to reset other state variables, if any (e.g., various flip-flops), to their conditions prior to entering *rnd*. In the B6700 implementation, all this return information, including that which we have called the return label, is constructed and saved by the processor in the first two slots (words) of the activation record.

Figure 3.4 Virtual processor with an associated operand stack.

Figure 3.5 Executing the functional reference to *rnd*, which is assumed to be declared within block A of the algorithm. Lines marked d are dynamic links. Lines marked s are static links.

Note that ep of the return label is the value of the dynamic chain link (dc) indicated as part of the record's link word.

2. Second, notice that the ip is now shown as the triple (1, 1, u). It was previously shown as a 2-tuple. This added detail is given to clarify the way program point addresses are defined, but not necessarily how program points are accessed. The first element identifies the table holding the target instruc-

#### 3.3 TREATMENT OF SYSTEM INTRINSICS

tion's segment descriptor (1 means segment dictionary; 0 means stack trunk). The next two elements identify the segment in terms of the offset (1) relative to the segment table (the segment dictionary in this case) and the offset (u) relative to the base of the target segment.

When execution "enters" a segment (i.e., when the hardware instruction *enter* is executed), one hardware register is loaded with the base address of the segment as extracted from its segment descriptor (found either in the segment dictionary or stack trunk) while another pair of hardware registers (not shown in our diagrams) is used as an instruction counter. (On each execution cycle, the hardware forms the byte address of the next instruction by summing the values of these registers.)

3. Third, observe that the activation record is dynamically linked to that of block C but statically linked to that of A, since *rnd* is declared in block A of the algorithm (shown in Figure 2.3). In contour terms, the accessing environment for *rnd* must be the one in which the record contour for *rnd* is (immediately) nested, and this contour is that of A. Observe how the EP display has been appropriately adjusted.

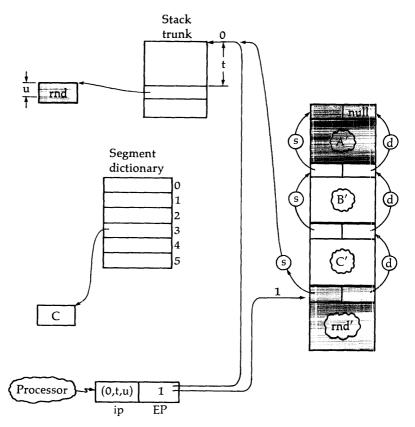

#### 3.3 TREATMENT OF SYSTEM INTRINSICS

Suppose that *rnd* were not declared within the algorithm as suggested in Figure 2.3 but rather that *rnd* is a function recognized by the compiler as a system routine (referred to in Burroughs literature as a *system intrinsic*), whose code segment is pointed to from the stack trunk. Figure 3.6 shows the data structure that would then be developed for execution within *rnd*. System intrinsics are treated as if declared within procedures that execute at display level zero. Hence, system intrinsics always execute at display level 1 (one level higher than the level of their declaration). Figure 3.6 thus shows that the activation record for *rnd* is statically linked to the stack trunk. To avoid cluttering the diagram, the static link from A' is not shown. That link also reaches the stack trunk, though indirectly, via a link word in the segment dictionary.

Figure 3.6 Executing the functional reference to *rnd*, which is assumed to be a *system intrinsic*. Lines marked (d) are dynamic links. Lines marked (s) are static links.

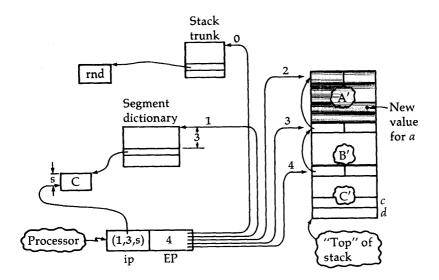

#### 3.4 BLOCK EXITS AND RETURNS

Figure 3.7 shows the snapshot taken just after completing execution of the statement labeled P. In returning from rnd the top pointer of the EP display is again at level 4, pointing at C'. In effect, the activation record, rnd', has been deallocated. The processor has stored a new value in the cell labeled a in the record A'. If any new temporaries are needed in the course of executing other state-

Figure 3.7 After completing execution of the statement labeled P.

ments in block C, they will be pushed onto the top of the stack as part of C' (where the record rnd' once resided).

Notice that a return from a function call (and the same would be true for a simple exit from a block) is accompanied by what can be interpreted as an act of deallocation. In Algol 60-like languages, this association of deallocation with returns (or exits) has its roots in the semantics of the language [37, 44, 58]. Note, for instance, that after return from *rnd* to block C the data items kept in rnd' are no longer "defined." Conceptually, such undefined items are no longer accessible to the processor. An act of deallocation, done by nullifying the processor's top display register, as in a simple block exit, is tantamount to making the record for that block inaccessible.

#### 3.5 PROCEDURE CALLS—GENERAL

The approach to procedure call implementation has already been introduced indirectly in the foregoing discussions of Figures 3.5–3.7. Here we take a head-on look at the subject.

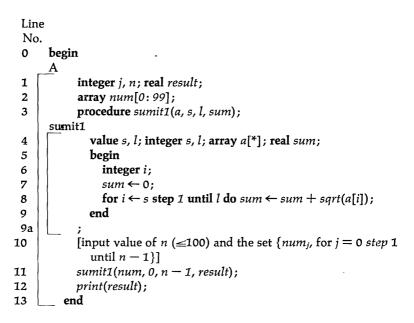

We select another model program, Figure 3.8, as a basis for dis-

Figure 3.8 Program for use in discussing procedure calls. Scoping lines at the left of the code are labeled A and sumit1 to correspond with the blocks of the program.

cussion. The program shows one explicit procedure call on the system's intrinsic *sqrt* and another on the declared procedure *sumit1*. Whether declared explicitly or implicitly, the compiler must generate a calling sequence that includes a reference to the target (procedure) segment. When executed, this reference is employed in an attempt by the processor to gain execution access to the target. Since it is the record of execution that defines the valid accessing environment for the processor, the compiler must specify the pointers to all called procedures such that during execution these pointers may be appropriately placed within the proper activation record used by the processor. The B6700 way of reaching this objective is suggested by a snapshot series shown in Figures 3.9–3.11 for the case where execution of the algorithm in Figure 3.8 is about to execute line 11, is about to execute line 9, and is about to complete execution of line 12, respectively.

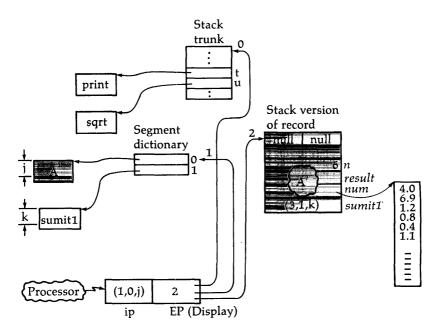

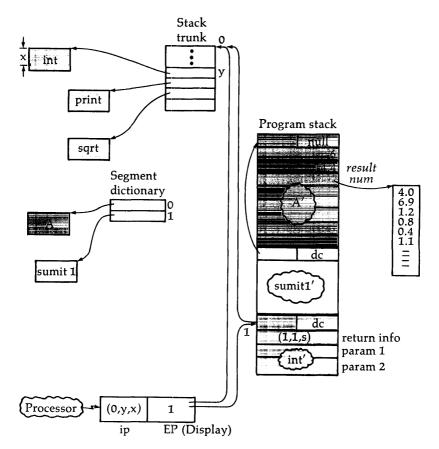

Figure 3.9 Snapshot of Figure 3.8 program execution just before executing line 11. Six data values for the *num* array are assumed to have been input as a result of executing line 10. (The symbols k and j represent entry-point offsets within the code segments for *sumit1* and block A, while the symbols t and u represent offsets within the stack trunk.)

Upon entering block A, the record A' that is placed in the stack must (among other things) include pointers to all procedures that are explicitly declared in block A of the algorithm, i.e., the pointer to *sumit1*. Each such pointer is in essence an (ip, ep) label pair. The environment pointer component of the label defines the immediate environment within which the target procedure is to execute. In the B6700 representation, explicit ep values are, however, unnecessary, since the positioning of each procedure pointer within its appropriate activation record is tantamount to defining the addressing environments of the respective procedures.

Thus, the procedure pointer for *sumit1*, located in the activation record A' and shown (3, 1, k), in essence specifies the display level

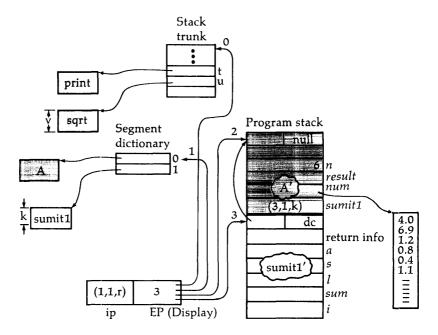

Figure 3.10 Snapshot of Figure 3.8 program execution just before executing line 9. (Symbols k and v represent entry-point offsets; symbol r represents the offset for the current instruction within the code for *sumit1*; and symbols t and u represent offsets within the stack trunk.)

(3) at which *sumit1* will execute, the segment number (1), and offset (k) within the algorithm's code file. The segment number (1) gives the offset (always) in the segment dictionary where the segment descriptor for the target segment can be found. Readers should note that although the procedure pointer triplet, e.g., (3, 1, k) and the ip triplet, e.g., (1, 1, r) have for convenience been shown in similar syntax, their respective semantics are different.

In addition to the link word, called a Mark Stack Control Word, or MSCW in B6700 terminology, each activation record contains a word of return information, called a Return Control Word (RCW), immediately following the link word. The return label consists of an (ip, ep) pair, where the ip is contained within the RCW and the ep is in essence the dynamic link, dc, of the MSCW.

*Figure 3.11* Snapshot of Figure 3.8 program execution just before completing the execution of line 12. (Shading for certain of the blocks is discussed in Section 3.7.)

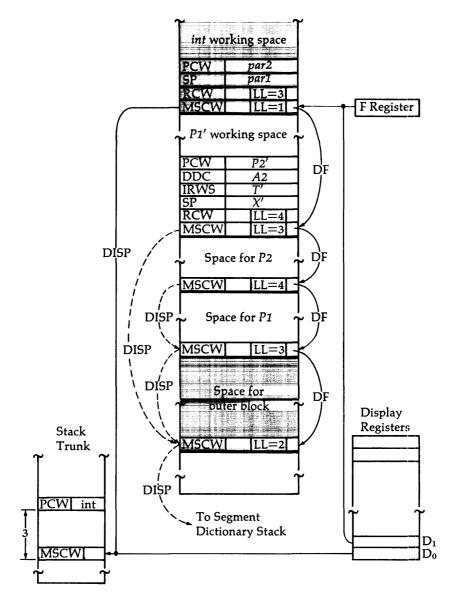

# 3.6 HARDWARE INTERRUPTS AS HARDWARE-FABRICATED PROCEDURE CALLS

Perhaps the most significant simplifying design achievement of the B6700 has been the natural exploitation of the stack structure just described for the handling of hardware interrupts. Such interrupts were viewed conceptually by the B6700 designers to be merely unexpected procedure calls. This view has been fully realized.

When an interrupt signal is sensed by a hardware processor, it executes (through microcode) an enter instruction to a standard instruction address (ip) after first pushing a hardware-fabricated activation record onto the stack currently employed by that processor. The net effect is that when the "called" interrupt handler begins executing, it does so with a well-formed record of execution. That record is linked dynamically to the record of the interrupted procedure. Return information in the new record points back to the ip which represents the next instruction that would have been executed had not the interrupt occurred, and the formal parameters within the activation record have been given hardware-supplied values that define the nature of the interrupt.

The interrupt routine can examine the parameters and on the basis of their values call "specialist" handler routines for further processing, as required. If the special routines execute returns to the primary (system) interrupt handler, the latter will in turn execute a return to its "caller," which in this case is the interrupted procedure.

System interrupts need have nothing to do with the current program. The interrupt may, for example, represent an I/O complete signal that is quite independent of this computation. On the other hand, process interrupts (related to this task) such as arithmetic overflow, divide check, presence bit, etc. can also be processed effectively. In either case the interrupt routine executes at display level 1.

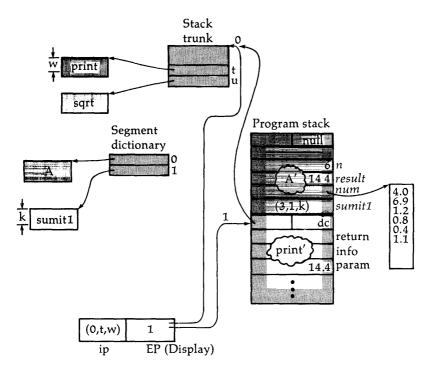

By using the present stack and fabricating ordinary procedure calls in the manner just described, there is minimum overhead cost expended in saving and restoring the state of the interrupted program. Figure 3.12 shows snapshots immediately after a system interrupt that is assumed to occur just before executing line 9 of the Figure 3.8 program. The (assumed) name of the system interrupt routine is *int*. Figure 3.12 may be compared with the snapshot in Figure 3.10 which is the situation immediately before the assumed interrupt.

## 3.7 SMALL WORKING SETS

A few other observations concerning the B6700 data structure are in order here. Note that the *num* array is not allocated as part of the stack structure. Only a descriptor to this array is kept (in

Figure 3.12 Snapshot of Figure 3.8 program executing after a system interrupt while the processor was getting ready to execute line 9. (See Figure 3.10 for snapshot immediately prior to this interrupt.) The interrupt procedure *int* executes at display level 1. Its activation record is statically linked to the stack trunk where it can access procedure pointers to other system procedures "declared" at level 0.

the record for block A). Since all references to the *num* array's elements must be made (indirectly) via the array descriptor, and since this descriptor has a presence bit that is sensed by the hardware, then the array itself need be present in core memory only when the

program is making frequent references to it. By allocating data arrays and the stack segment separately, the stack can be kept small in size, thus minimizing the amount of core storage required for the record of execution in order to run the program.

This raises the interesting question: Just what portion of the job's address space does need to be present in core memory for effective execution? Well, of course, the answer must be phrased in terms of a particular snapshot of that job's execution.

Common to every job's execution there is some group of key supervisory procedure and data segments that will always be retained in core. These include the interrupt handlers, etc., memory allocation routines, perhaps some key I/O routines, all supposedly pointed to from the stack trunk. Apart from these "wired down" segments, what else?

We illustrate with the case shown in Figure 3.11. Shaded segments represent portions of the address space that must be kept in memory at the instant of that snapshot (for that program). Note the key roles played by the stack trunk, the segment dictionary, and the stack segment, in keeping the working set so compact. In essence, these three segments hold the descriptors (with presence bits) that point to all other segments that may be referenced by the job at this time. A descriptor is so formatted that if its presence bit is off, the remainder of the descriptor contains enough information to locate the missing segment (on disk) without first consulting intermediate tables of referenced information.

The stack trunk, though large, is actually shared by all jobs, and the segment dictionary is quite small for small programs, e.g., student programs. The minimum working set size, therefore, is determined mainly by the current size of the stack segment and the size of the currently executing program block. As a practical matter, however, the working set would also include those segments of the program and those system intrinsics that are frequently executed in the current flow-of-control pattern followed by the job—and also any arrays or portions thereof which may be frequently referenced.

Primary descriptors to arrays (and to other structured variables) are kept in the activation record. But the descriptors to substructures (also with presence bit sensitivity) are kept in intermediate arrays, i.e., "dope vectors" for the case of two-dimensional arrays. Treating arrays in this fashion tends to keep to a minimum the por-

#### 3.8 SHARING PROGRAMS AND DATA

tion of an array (or other structure) that must be kept in core at any one time. Readers will note that many hardware paging techniques [23] also permit the subdividing of arrays into blocks, not all of which need be allocated concurrently in primary memory. But, such paging techniques are usually restricted to a fixed number of fixedsize blocks, whereas the B6700 system permits use of blocks whose number and size are arbitrary (and hence, blocks that can more closely match the actual structure of the array).

## 3.8 SHARING PROGRAMS AND DATA

To judge the incremental demand for core memory placed on the system by a job like that pictured in Figures 3.8–3.11, one needs to keep in mind several possibilities for program and data sharing in the B6700 (more sharing means lower incremental demands for core memory):

- 1. Two or more jobs may execute using the same algorithm (but on different data). For instance, one can picture several requests for printouts of current stock quotations (or current bank balances). Jobs for the several customers, each requesting that identical programs (code files) be executed, get to use the same segment dictionary and, of course, the same code segments. To be sure, the individual jobs have different execution stacks (records of execution). Since the code is pure and reentrant, there need be no synchronization among jobs that use identical "code files." The average working set size for such filial jobs (or rather, Siamese twins, triplets, etc.) tends to decrease with the size (number of jobs) of the "filial set."

- 2. Jobs may also share data arrays in three ways:

- (a) Descriptors for read-only data segments may be kept in the segment dictionary and hence shared by members of a filial set of jobs as with procedures. Depending on the block structure of a single job, such data segments may also be shared among tasks of the same job.

- (b) Any data array, read-only or otherwise, can be shared among separate sibling tasks within a single job if their separate execution stacks were passed the same descriptor from their father task. Here again, such sharing, whenever it is frequent, serves to lower the average (effective) working set size of jobs or tasks.

- (c) A task "budded" at any level has access to any descriptor owned by a (static) ancestor task at any lower level. It therefore has access to any information referenced by such a descriptor. This concept is illustrated in the next case study (in Chapter 4), where we consider two tasks within the same job that share the same array.

When data arrays are shared through different stack-based descriptors, special B6700 hardware operators are employed to give partial assistance in record-keeping, i.e., to see that descriptors to the same array are all properly updated whenever the location of the array or its attributes, e.g., its size, or its very existence, is altered. CHAPTER 4

# Tasking

## 4.1 CREATION AND COORDINATION OF TASKS

A specific example of a program that gains a second site of activity is illustrated in Figure 4.1. The overall objective of the algorithm in this figure is identical with that of the Figure 3.8 algorithm, but the internal structure is modified so that half the work of summing is delegated to an offspring task that functions asynchronously (e.g., can in principle function concurrently) with the principal task.

Lines 3, 5, 10, 14, and 16 reflect most of the new syntactical units required to achieve a simple, synchronized, tasking objective. At line 3 a variable, ev1, of type **event** is declared for use as the basis for synchronization. A matching formal parameter called *done* is declared in line 5 for the procedure *sumit2*. (Line 3 declares a null event that serves as a "syntactical dummy." We imagine it is required for matching *done* in the call on line 15.)

To request that *sumit2* be executed as a separate (but related) task, a new syntactical construction is needed. Burroughs Algol [12], for instance, employs the key word **process** to distinguish a task call (line 14) from an ordinary procedure call (line 15). The task call passes the actual parameter ev1 (by reference) to *sumit2*, so that the offspring task, an instance of *sumit2*, may signal the main task when the former has completed its work. The B6700

| Line |                                                                                                                                                        |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| No.  |                                                                                                                                                        |

| 0    | begin                                                                                                                                                  |

| 1    | <pre>integer j, n; real result1, result2;</pre>                                                                                                        |

| 2    | <b>array</b> num[0: 99];                                                                                                                               |

| 3    | event ev1, null;                                                                                                                                       |

| 4    | <pre>procedure sumit2(a, s, l, sum, done);</pre>                                                                                                       |

| 5    | <b>value</b> <i>s</i> , <i>l</i> ; <b>integer</b> <i>s</i> , <i>l</i> ; <b>real</b> <i>sum</i> ; <b>array</b> <i>a</i> [*]; <b>event</b> <i>done</i> ; |

| 6    | begin                                                                                                                                                  |

| 7    | integer i;                                                                                                                                             |

| 8    | $sum \leftarrow 0;$                                                                                                                                    |

| 9    | for $i \leftarrow s$ step 1 until l do $sum \leftarrow sum + sqrt(a[i]);$                                                                              |

| 10   | cause(done);                                                                                                                                           |

| 11   | end sumit2                                                                                                                                             |

| 12   | ;                                                                                                                                                      |

| 13   | [input value for $n \leq 50$ and $\{num_j, \text{ for } j = 0 \text{ step 1 until} \}$                                                                 |

|      | $2 \times n-1$ ]                                                                                                                                       |

| 14   | <b>process</b> sumit2(num, n, $2 \times n - 1$ , result2, ev1);                                                                                        |

| 15   | sumit2(num, 0, n — 1, result1, null);                                                                                                                  |

| 16   | wait(ev1);                                                                                                                                             |

| 17   | print(result1 + result2);                                                                                                                              |

| 18   | end                                                                                                                                                    |

*Figure 4.1* Program for use in discussing multiple sites of activity. Shaded sections reflect new syntactical units required to achieve a simple, synchronized tasking objective.

system intrinsic *cause* (on line 10) is used for this purpose. After executing the ordinary procedure call to *sumit2*, and passing it a null reference for the formal parameter, *done*, the main task executes a call to the system intrinsic *wait* (on line 16). *Wait* returns to its caller when and if the actual parameter, *ev1*, attains a value that may be interpreted as: "The event has happened." Upon return from *wait*, the algorithm calls for the printout of the sum of two values, *result1* and *result2*, each value representing half of the required work (the first half having been accomplished by the main task and the second half having been accomplished by the offspring task).

Variables of type event are structured. One field in this structure

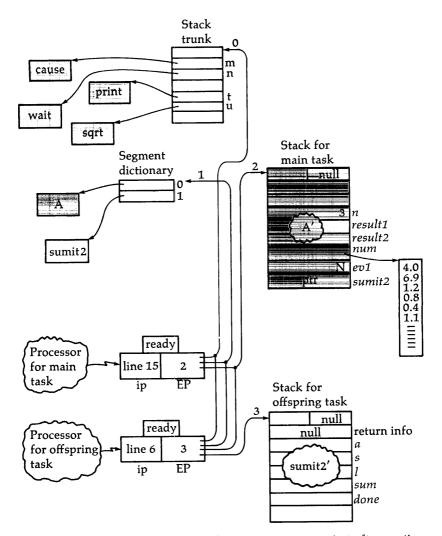

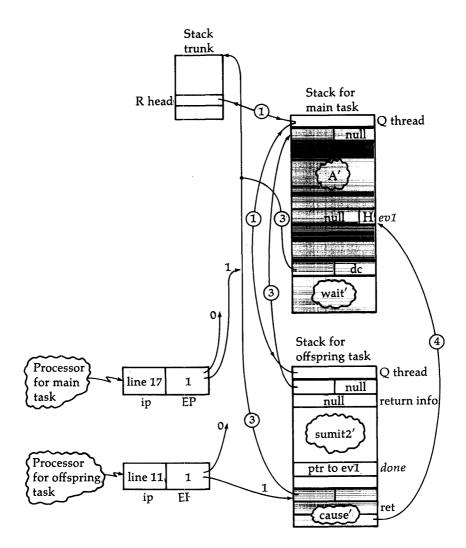

Figure 4.2 Simplified snapshot of the Figure 4.1 program just after creating the offspring task (at line 14). (The symbol ptr represents a procedure pointer whose form is discussed in Section 3.5.)

is a binary switch called the "happened" bit, which is set to *not* happened initially and later set to happened when the cause intrinsic is executed. The rest of the structure for an event variable is best explained in terms of several execution snapshots. These snapshots and the accompanying discussion are provided to illuminate the semantics of tasking.

Figure 4.2 gives a snapshot of the Figure 4.1 program just after the main task has created its offspring. The processor for the main task is pictured as about to execute line 15 of the program while the processor for the offspring is pictured as about to execute line 6. Each has its own EP display, the one for the offspring being—in this rather simple example—a copy of the parent's display to which has been adjoined a display element that points to the new task's "very own" stack at level 3.

The processors depicted in Figure 4.2 are virtual ones. They may or may not be currently mapped on to actual B6700 CPU's. In any case, they are *ready* to be so mapped, i.e., ready to run, whenever this form of physical activation can be accomplished. The execution state (variable) of a virtual processor, e.g., ready or waiting for some event to happen, can be thought of as attached to the processor, as suggested in Figure 4.2 or, as in Figure 4.3, to the stack of the task it now "serves."

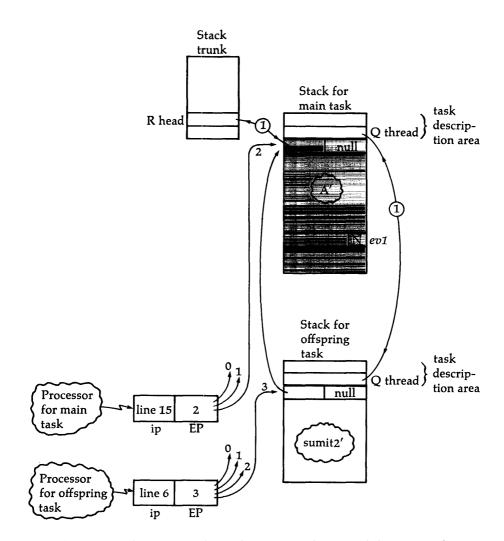

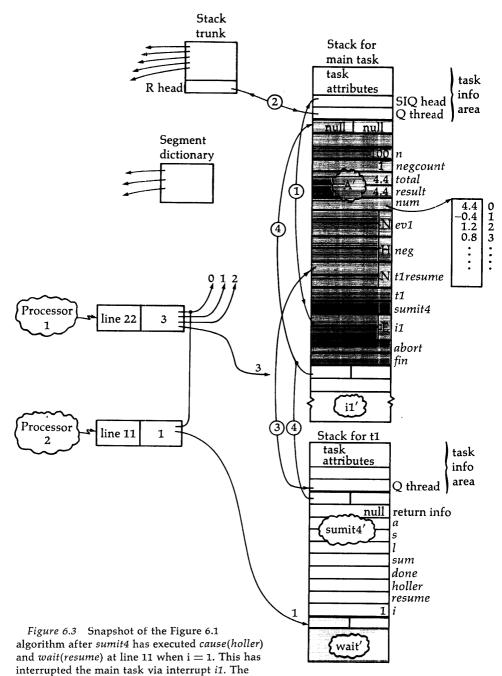

Figure 4.3 reflects the actual B6700 implementation. The stack created for each new task begins with a task description area (of fixed size), following which is placed the first activation record. A combination of hardware and system software prevents access to this area except by supervisory programs. One of the key pieces of information in this special stack area is a thread (Q) by which a task may be linked to a list head that defines the queue state of the task. If the task is *ready*, Q thread is link-listed (lines marked (1)) to a ready (R) head located in the stack trunk. Employing this list the system supervisor is able to choose (schedule) tasks to be run.

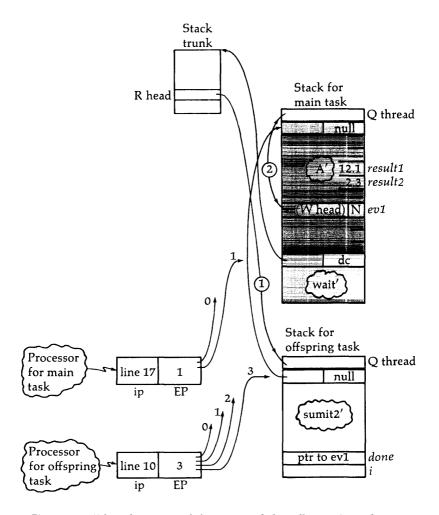

Figures 4.4–4.6 picture three possible snapshots of subsequent execution. In Figure 4.4 it is presumed that the main task has "speeded" through its work faster than its offspring, so the main task has reached and has executed line 16 while the offspring is just now reaching the *cause* at line 10. Figure 4.5 shows the effect

Figure 4.3 Showing how the stack for each task is threaded onto a ready list (lines marked ①), the head of which, R head, is kept in the stack trunk. Threading for each task is through a (one-per-task) queue thread (Q thread).

Figure 4.4 When the main task has executed the call to *wait* on the occurrence of event ev1, whose value is "N" (for *not happened*), the Q thread for the main task's stack is disconnected from the ready list and threaded onto a wait list, whose head word (W head) is in ev1. (See the line marked ③.) Only the offspring task about to execute line 10 remains connected to the ready list (line ①).

Figure 4.5 The offspring task, by executing in *cause*, has changed the value of the event variable ev1 to "H" for happened via the parameter done that was passed to *cause* as an argument. (See line marked ④.) The main task will now be able to resume by returning from *wait*. Lines marked ③ indicate various static links.

of the offspring having executed line 10 but not line 11. Figure 4.6 shows the effect of the offspring having executed line 12, i.e., exit from *sumit2*, which, in the case of a task, amounts to task termination, since the return label is null.

In Figure 4.4 we see what happens when a task executes a *wait* intrinsic and the named event has not happened ("N").

The main task has executed

wait(ev1);

When *wait* discovers that the value of ev1 is "N," the Q-thread element is deleted from the ready Q (line ①) and linked into a wait queue whose head is a substructure of the ev1 variable (line ②).

In Figure 4.5 we see what happens when a task *causes* an event. The *cause* intrinsic gets a copy of the value of *done* as its parameter, which, in turn, is a pointer to the (globally defined) variable ev1; *cause* has no trouble setting ev1's happened state to *happened* (line ④). As a second step, *cause*, which is privileged to tinker with the Q threads, rethreads the main task's Q thread onto the ready list (line ①). Lines marked ③ in this figure are static links that define the respective addressing environments of the two tasks.

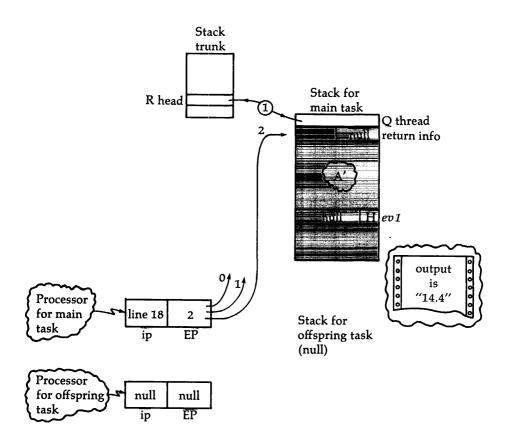

The return label for *sumit2* in the offspring stack has been marked null to suggest task termination when the processor for the offspring executes the procedure exit at line 12. In concept, such an exit is equivalent to a **go to** *null* statement. In the actual B6700 implementation the return slot of the first activation record of every task is not given a null value, but rather the entry point of a system control procedure (whose own activation record is then fabricated and pushed onto the stack trunk). This system procedure deallocates the task's stack (and any other resources associated exclusively with this stack) and thus terminates the task. Figure 4.6 is, therefore, a stylistic interpretation to connote the offspring task's demise.

## 4.2 TASK ATTRIBUTES

To gain greater control and/or communication among a family of tasks (those "started" by and including a common ancestor),

*Figure 4.6* The offspring task has reached its terminus by executing line 12. Its ip and EP values are now (effectively) null. The main task has printed the results referred to in line 17 and is about to execute line 18 which will be its terminus (a block exit for which ip and EP are both effectively null).

each task is endowed with a structured *task* variable whose components define various attributes of the task.

The task variable is associated with the task at its creation and a syntactical facility has been provided to achieve this objective. Thus, strictly speaking line 14 of the Figure 4.1 algorithm was improperly coded since no task identifier variable was indicated to be associated with the created offspring task. A correct coding in Burroughs Algol would require that line 14 be coded, for instance, as:

**process** summit2(num, n,  $2 \times n - 1$ , result2, ev1) [charlie];

Moreover, an appropriate declaration, i.e.,

would be inserted, say at line 2.5, to indicate that the identifier charlie is a variable of type **task**.

The task variable has a fixed structure so that it can be and is allocated into the task information area of the task's stack at the time the task is born.

Although the task information area is normally off limits in the accessing sense, tasks are afforded controlled access to the task variable substructure via what amount to "caretaker" intrinsics. Some task attributes are given initial values that are fixed for the life of the task. Others may be altered by the task itself, while still other attributes of a task may be altered only by certain other tasks of the family, e.g., parents.

A selected subset of the task attributes that are employed in the current B6700 implementation is discussed here. For convenience, the description is given in terms of the syntax now employed in Burroughs Algol.

Suppose a main task is coded to create an offspring and later make reference to task attributes of that offspring. Code such as the following might then appear in the main task portion of the algorithm.

Line No. 2.5 task charlie; 14 process sumit2(num, 2,  $2 \times n - 1$ , result2, ev1) [charlie];

In addition, various attributes could be assigned to *charlie* before it is started. For example:

Line No. 12.1 charlie.priority  $\leftarrow 5$ ; 12.2 charlie.maxproctime  $\leftarrow 20$ ; comment in seconds; 12.3 charlie.stacksize  $\leftarrow 2^8$ ;

Lines 12.1–12.3 are intended to suggest that the system recognizes a subset of task attributes, initial values for which can be supplied by the creator task. Values for these attributes can then be noted and employed by the system's scheduling algorithm or other resource management modules. When any job is initiated, initial attributes for the main and/or only task of that job may be supplied by the user via control cards (i.e., at command level). In this way the user may specify attributes of his main task just as code in the main task may specify initial attributes for its offspring, or offspring for its offspring, etc.

The attribute *status* reflects the current execution state of the task [e.g., scheduled, running (active), suspended, terminated]. This attribute can be queried by any task in the family for which the task identifier (*charlie*) is "visible," e.g., its creator, itself, or any descendants for which *charlie* is global. In addition, these same tasks are able to write in the status variable, thus forcing *charlie* to be suspended, terminated, etc.

Some task attributes are provided so the system can log operational information, e.g., processor time and I/O time so far expended, time of day that the task was begun, etc.

Several key attributes have been defined for tasks to be used in achieving special interrelationships among tasks. Four of these attributes are *status*, *exceptiontask*, *exceptionevent*, and *partner*. They are explained here and their use is illustrated in Section 4.3.

Exceptiontask and exceptionevent are used, for instance, to alert a task, A, that there has been a status change for a given (descendant) task, B, or for any of a group of (descendant) tasks, B, C, D, etc.

To see how each of these attributes is employed, suppose we imagine that task *A* causes a change in its own status attribute, using the known task id, *myself*, e.g.,

The immediate effect of this statement is merely to request (of the system) a change of the task's status attribute to a new code value. But, eventually, the system's scheduling machinery will take note of this request (when it next attempts to ready task A, assuming some time-sharing or multiprocessing discipline is governing) at which time the system will change the status value of task A and will actually suspend task A. (Only another task that is apprised of this suspension can reverse this action.)

The system reacts as follows upon noticing a change in task A's status: Task A's exceptiontask attribute, which is interpreted as a task identifier, is used by the system to *notify* that target (task) of the status change for A. Let the target task so identified be task B, which is perhaps the immediate ancestor of task A. Now, task B has associated with it its own structured task variable, one of whose components is *B.exceptionevent*. This component is an event variable (automatically declared and initialized to "N" by the system). Upon noticing a change in status for A, the system causes B.excep*tionevent*, i.e., the exceptionevent "belonging" to the task designated by A.exceptiontask. If B had been waiting for this event, B would now be readied and allowed to resume. Note that any other tasks that happen to be O-threaded, i.e., wait-listed, on *B.exceptionevent* will be correspondingly alerted. Thus, the net effect of a *myself*. status change can be to alert a series of other tasks (broadcast) that may be waiting to learn of this occurrence. In Chapter 6, when we discuss software interrupts, we will see then that an alternative effect of *cause*ing an exceptionevent can be to have the notification take the form of interrupts.

In the B6700 implementation, the task that starts *charlie* (or any task that can "see" *charlie*'s task variable) can act like *charlie*'s supervisor or big brother, because such a task (besides *charlie* himself) can write as well as read *charlie*'s status attribute. Let *pete* be any task that can see *charlie*'s task variable. Then:

- 1. Depending on *charlie's* status, *pete* can activate, suspend, or terminate *charlie*.

- 2. If *charlie* has been suspended by virtue of executing a condition handler invoked by some hardware-detected processing

fault, e.g., a floating point overflow, *pete* can read some of *charlie*'s attributes and attempt a diagnosis of the trouble. Among the attributes that are useful for such diagnosis is the *stoppoint* attribute, which is the ip of the (*charlie*'s) last executed instruction.

We see that *pete* is able to control *charlie*'s execution state via *charlie.status* and *charlie* can alert *pete* to a change in the former's status.

If no initial value is assigned to *charlie.exceptiontask*, then *pete*, the task that starts *charlie*, is the exceptiontask for *charlie* by default. But note that *charlie.exceptiontask* can be altered afterwards, either by *pete* or by *charlie* himself. Thus, in the latter case, a statement like

### *myself.exceptiontask* $\leftarrow$ *brothertom*;

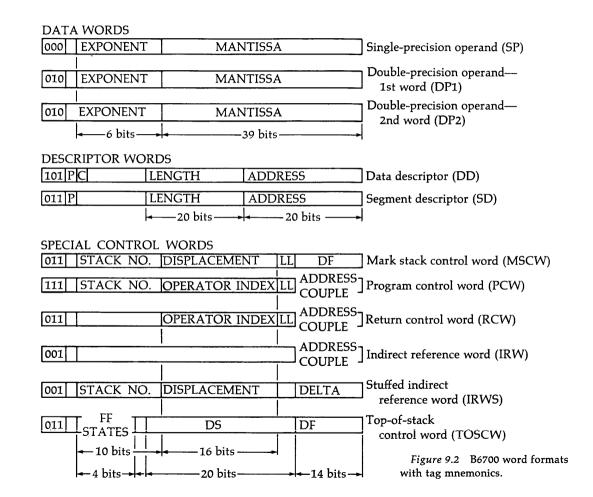

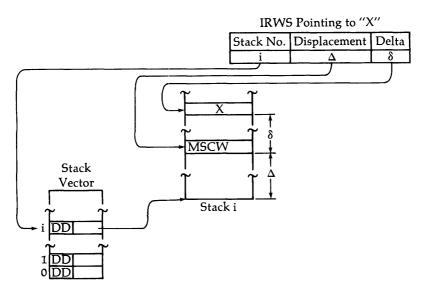

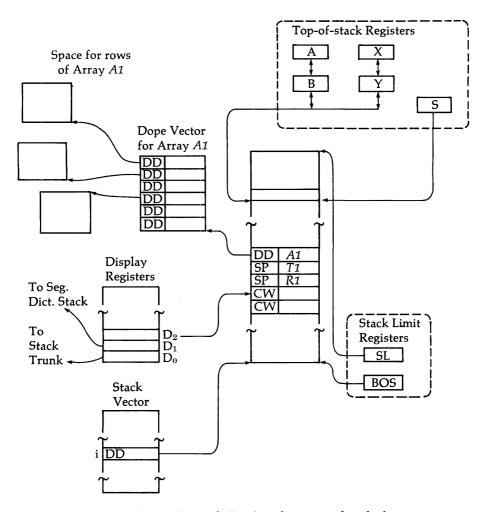

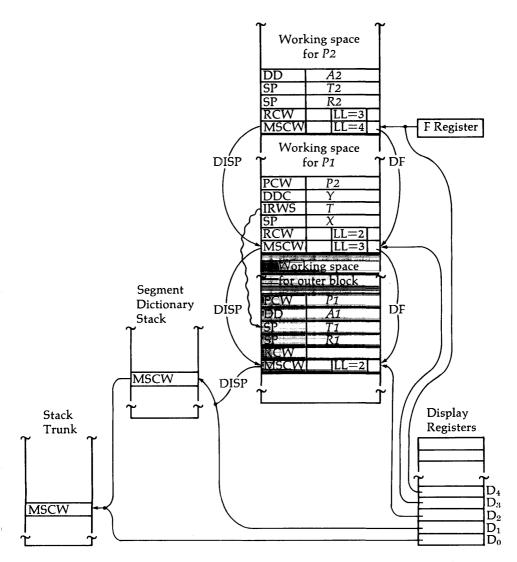

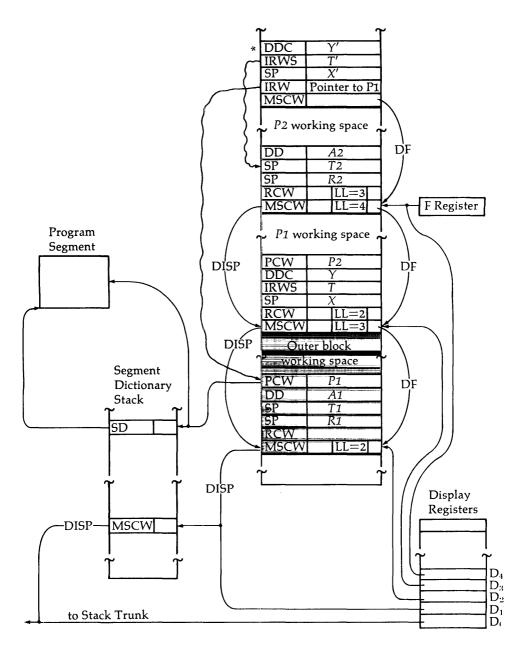

is a way for *charlie* to let the task named *brothertom* "look after him." The intent of such a statement is equivalent to, "In case I am suspended, do not tell my parent, tell brothertom." In this way, two or more tasks can establish one another as watchguard of one another (e.g., *A* is the exceptiontask for *B*, and vice versa).